給VCXO選擇石英晶體的用處

來源:http://www.yphwp.cn 作者:金洛鑫電子 2019年04月02

無源的石英晶體是比較常見的頻率控制元器件,VCXO晶振雖然不罕見,但是一直以來并沒有像Crystal那么普及,因為VCXO的成本高,性能好,適用于中高端的科技多功能產品身上。Voltage controlled crystal oscillator的中文意思是壓控晶體振蕩器,具有特殊的電壓控制功能,有多種不同的應用,其中一種叫做鎖相環。為了使VCXO在鎖相環的電路板中,可以實現拉動石英晶體,使VCXO的輸入的可控制電壓,輸出的頻率可以成正比,實現PLL同步,上下轉向,穩定抖動,輸出參考頻率等目的,因此廠家需要為VCXO Oscillator選擇和指定符合的石英晶體。

水晶參數:

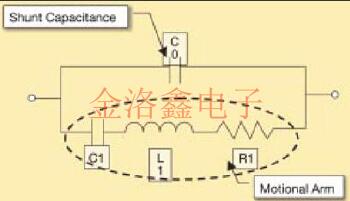

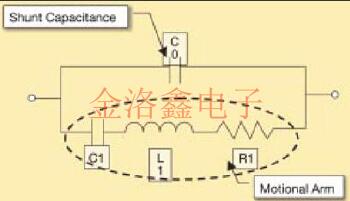

VCXO用于PLL應用,如圖1所示.VCXO中使用的石英晶體的等效電路如圖2所示.C1,L1和R1是晶體的運動參數,C0是并聯電容。C0實際上是-它實際上可以用一個簡單的電容表來測量。另一方面,運動臂參數是等效的并且不易測量。晶體的頻率下降多少取決于C0/C1的比例。

圖2.單模,單端口,晶體諧振器等效電路模型

圖2的阻抗方程為:

等式1很復雜,我們只對虛部感興趣,這被稱為晶體的反應曲線,如圖3所示。在圖3中,標記為fs的點是運動電容C1諧振并抵消運動電感L1的位置。在fs校準到所需頻率的晶體稱為串聯晶體。校準的晶體在平行區域工作。重要的是要注意,串聯和并聯晶體之間沒有區別,只有制造商校準它。 VCXO電路希望將負載電容(CL)與晶體的端子串聯。隨著負載電容的變化,晶體將通過改變其頻率來響應。這很棘手,并且在許多論文中都是錯誤的。電容負載始終與晶體串聯,絕不平行。換句話說,并聯晶體并不意味著與晶體并聯的電容器,而是串聯的。具有并聯晶體的系列中需要負載電容,以使頻率在校準容差范圍內。如上所述,隨著負載電容CL變化,晶體的頻率改變。實際上,它改變如下:

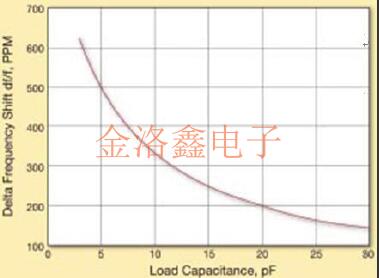

點fs,到一定的負載電容CL。等式2的曲線圖稱為圖2.從等式2可以看出,較大的C1是距離特定CL頻率的距離越大(拉動越多)。因此,對于VCXO晶振具有大的C1值是有利的。因此,等式2表明CL和C0需要盡可能小以最大化晶體上的拉力。事實證明,C1是C0的函數,C1不能增加C0。選擇CL值后,您只需將C0/C1的比率指定為完成的特定最大值。

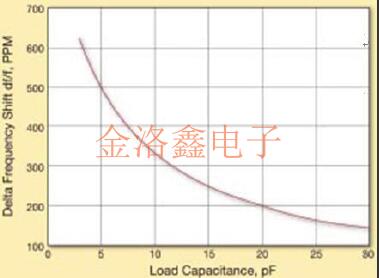

圖4.作為負載電容函數的C1=10fF和C0=5pF的晶體的拉曲線

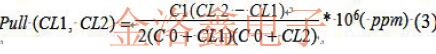

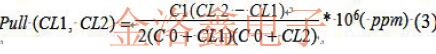

等式2的更有用的形式是從一個負載電容到另一個負載電容的牽引方程。那個公式是:

公式3的使用將在下面的VCXO設計實例中說明。

VCXO設計實例:

38.88MHz VCXO貼片晶振希望在PLL應用中使用,以同步到必須保持鎖定至少10年的輸入參考頻率。工作溫度環境為-10°C至+70°C。已知輸入參考電壓的總精度為20ppm。假設內部VCXO電路設計為當受控電壓(Vc)居中時,標稱負載電容(CLN)為14pF,低控制電壓和高控制電壓分別為8pF和27pF(CLL,CLH)。指定VCXO的所有必要晶振參數。

解決方案:

中心頻率:38.88MHz

負載能力:14pF

操作模式:(例如,“基本”或“第三泛音”。)石英晶振有多種響應(見圖5)。第一個主要反應叫做基礎。下一個主要的反應是第3次泛音,然后是第5次,依此類推;唯一的賠率。晶體沒有諧波,只有泛音。圖2可以通過為每個泛音響應添加額外的動作臂來擴展。泛音臂的運動電容將等于:

其中N是泛音數,C1是基波的運動電容。

例如,第三泛音運動電容等于基本響應的運動電容的九分之一。因為這個事實,很難拉上泛音水晶。因此,可拉動的晶體是基本的。

電阻:由于晶體是無源元件,因此必須通過Oscillator電路來克服。振蕩器電路設計者或芯片制造商有責任做出最大損失。如果你的電路在fs或串聯點運行晶體,如圖3所示,那么R1的值就是損耗。但是我們為這個例子指定了一個平行而不是一系列晶體,因為我們已經有14pF的負載電容。那么損失是什么,如果它不是R1?在并行區域,損失是CL和C0的函數,由下式給出:

其中E.S.R代表等效串聯電阻。用于E.S.R的一個很好的數字是最多50。校準或公差:這是頻率精度+25℃的晶體。制作此規格越嚴格,晶體的成本就越高。由于我們正在跟蹤輸入參考并且環路始終處于鎖定狀態,因此校準編號并不重要。最大25ppm的數字就足夠了。

分流電容,C0:在現代晶體中,這個數字總是如此最大7pF。或者,它可以與C0/C1的比率相關聯。

溫度范圍內的頻率穩定性:晶體會發生變化溫度:并且在-10℃至+70℃之間,不產生成本的良好數量為30ppm。

老化:諧振器頻率需要隨時間變化。一個好的規格是第一年5ppm,之后每年最多2ppm。

動態電容,C1:為了計算運動電容,我們首先需要弄清楚如何去做。最低要求是:

需要最小拉力=(輸入參考精度+晶體總誤差)其中晶體的總誤差=校準+穩定性+老化10年:

=25+30+(5+18)

=78ppm

因此,需要最小的拉力

=20+78

=98ppm

使用公式3并設置C0=7pF,計算C1的值 驅動電平不應過載:

從CLN=14pF到CLL=8pF,最小-98ppm。C1的相同值必須從CLN=14pF拉至+98ppm,至CLH=27pF。與C1=11個FF,我們得到的=-104.8ppm的從14pF到8PF和100.1ppm的從14pF到27皮法的拉力。因此,C1=11fF最小值,C0=7pF最大值將滿足所需的最小拉力。給自己一些額外的保證金并指定C1=15fF最小值。

切割水晶:(例如,AT-Cut或BT-Cut)。在水晶上切割到切割水晶毛坯的角度。切割角度主要影響溫度性能的穩定性。可拉制晶體由AT-Cut石英制成。BT-Cut晶體的頻率較低與AT切割相比,溫度穩定性更高。這種BTX切割可用作可拉動的壓電石英晶體。因此,請指定AT-Cut。

已經掌握規格的制造商,他們可以幫助選擇正確的包裝。對于需要在較大包裝中的可拉晶體尤其如此。在本例中,我們選擇了UM-1包。晶體的RMS功率可以在不破壞或經歷過度老化的情況下消散。振蕩器電路設計者或芯片制造商應說明驅動電平。封裝越小,驅動電平規格越低。對于UM-1封裝,500uW最大驅動器級別規格就足夠了。在確保晶體不會過載的過程中,應測量驅動電平。

從目前掌握的資料來看,為應用到鎖相環的VCXO晶振指定合適的晶體,已是一項比較完善成熟的技術,解決了選型的問題,在這過程中使用了數學和方程學。VCXO Oscillator知名的制造商有愛普生晶振,Crystek晶振,KDS晶振,TXC晶振,加高晶振,CTS晶振,ECS晶振,ABRACON晶振等品牌。

VCXO用于PLL應用,如圖1所示.VCXO中使用的石英晶體的等效電路如圖2所示.C1,L1和R1是晶體的運動參數,C0是并聯電容。C0實際上是-它實際上可以用一個簡單的電容表來測量。另一方面,運動臂參數是等效的并且不易測量。晶體的頻率下降多少取決于C0/C1的比例。

圖2.單模,單端口,晶體諧振器等效電路模型

等式1很復雜,我們只對虛部感興趣,這被稱為晶體的反應曲線,如圖3所示。在圖3中,標記為fs的點是運動電容C1諧振并抵消運動電感L1的位置。在fs校準到所需頻率的晶體稱為串聯晶體。校準的晶體在平行區域工作。重要的是要注意,串聯和并聯晶體之間沒有區別,只有制造商校準它。 VCXO電路希望將負載電容(CL)與晶體的端子串聯。隨著負載電容的變化,晶體將通過改變其頻率來響應。這很棘手,并且在許多論文中都是錯誤的。電容負載始終與晶體串聯,絕不平行。換句話說,并聯晶體并不意味著與晶體并聯的電容器,而是串聯的。具有并聯晶體的系列中需要負載電容,以使頻率在校準容差范圍內。如上所述,隨著負載電容CL變化,晶體的頻率改變。實際上,它改變如下:

點fs,到一定的負載電容CL。等式2的曲線圖稱為圖2.從等式2可以看出,較大的C1是距離特定CL頻率的距離越大(拉動越多)。因此,對于VCXO晶振具有大的C1值是有利的。因此,等式2表明CL和C0需要盡可能小以最大化晶體上的拉力。事實證明,C1是C0的函數,C1不能增加C0。選擇CL值后,您只需將C0/C1的比率指定為完成的特定最大值。

圖4.作為負載電容函數的C1=10fF和C0=5pF的晶體的拉曲線

公式3的使用將在下面的VCXO設計實例中說明。

VCXO設計實例:

38.88MHz VCXO貼片晶振希望在PLL應用中使用,以同步到必須保持鎖定至少10年的輸入參考頻率。工作溫度環境為-10°C至+70°C。已知輸入參考電壓的總精度為20ppm。假設內部VCXO電路設計為當受控電壓(Vc)居中時,標稱負載電容(CLN)為14pF,低控制電壓和高控制電壓分別為8pF和27pF(CLL,CLH)。指定VCXO的所有必要晶振參數。

解決方案:

中心頻率:38.88MHz

負載能力:14pF

操作模式:(例如,“基本”或“第三泛音”。)石英晶振有多種響應(見圖5)。第一個主要反應叫做基礎。下一個主要的反應是第3次泛音,然后是第5次,依此類推;唯一的賠率。晶體沒有諧波,只有泛音。圖2可以通過為每個泛音響應添加額外的動作臂來擴展。泛音臂的運動電容將等于:

其中N是泛音數,C1是基波的運動電容。

例如,第三泛音運動電容等于基本響應的運動電容的九分之一。因為這個事實,很難拉上泛音水晶。因此,可拉動的晶體是基本的。

電阻:由于晶體是無源元件,因此必須通過Oscillator電路來克服。振蕩器電路設計者或芯片制造商有責任做出最大損失。如果你的電路在fs或串聯點運行晶體,如圖3所示,那么R1的值就是損耗。但是我們為這個例子指定了一個平行而不是一系列晶體,因為我們已經有14pF的負載電容。那么損失是什么,如果它不是R1?在并行區域,損失是CL和C0的函數,由下式給出:

其中E.S.R代表等效串聯電阻。用于E.S.R的一個很好的數字是最多50。校準或公差:這是頻率精度+25℃的晶體。制作此規格越嚴格,晶體的成本就越高。由于我們正在跟蹤輸入參考并且環路始終處于鎖定狀態,因此校準編號并不重要。最大25ppm的數字就足夠了。

分流電容,C0:在現代晶體中,這個數字總是如此最大7pF。或者,它可以與C0/C1的比率相關聯。

溫度范圍內的頻率穩定性:晶體會發生變化溫度:并且在-10℃至+70℃之間,不產生成本的良好數量為30ppm。

老化:諧振器頻率需要隨時間變化。一個好的規格是第一年5ppm,之后每年最多2ppm。

動態電容,C1:為了計算運動電容,我們首先需要弄清楚如何去做。最低要求是:

需要最小拉力=(輸入參考精度+晶體總誤差)其中晶體的總誤差=校準+穩定性+老化10年:

=25+30+(5+18)

=78ppm

因此,需要最小的拉力

=20+78

=98ppm

使用公式3并設置C0=7pF,計算C1的值 驅動電平不應過載:

從CLN=14pF到CLL=8pF,最小-98ppm。C1的相同值必須從CLN=14pF拉至+98ppm,至CLH=27pF。與C1=11個FF,我們得到的=-104.8ppm的從14pF到8PF和100.1ppm的從14pF到27皮法的拉力。因此,C1=11fF最小值,C0=7pF最大值將滿足所需的最小拉力。給自己一些額外的保證金并指定C1=15fF最小值。

切割水晶:(例如,AT-Cut或BT-Cut)。在水晶上切割到切割水晶毛坯的角度。切割角度主要影響溫度性能的穩定性。可拉制晶體由AT-Cut石英制成。BT-Cut晶體的頻率較低與AT切割相比,溫度穩定性更高。這種BTX切割可用作可拉動的壓電石英晶體。因此,請指定AT-Cut。

已經掌握規格的制造商,他們可以幫助選擇正確的包裝。對于需要在較大包裝中的可拉晶體尤其如此。在本例中,我們選擇了UM-1包。晶體的RMS功率可以在不破壞或經歷過度老化的情況下消散。振蕩器電路設計者或芯片制造商應說明驅動電平。封裝越小,驅動電平規格越低。對于UM-1封裝,500uW最大驅動器級別規格就足夠了。在確保晶體不會過載的過程中,應測量驅動電平。

從目前掌握的資料來看,為應用到鎖相環的VCXO晶振指定合適的晶體,已是一項比較完善成熟的技術,解決了選型的問題,在這過程中使用了數學和方程學。VCXO Oscillator知名的制造商有愛普生晶振,Crystek晶振,KDS晶振,TXC晶振,加高晶振,CTS晶振,ECS晶振,ABRACON晶振等品牌。

正在載入評論數據...

相關資訊

- [2023-06-29]-40~+105°C時的6G貼片石英晶體...

- [2020-07-16]通信網絡時鐘系統7x5mm溫補晶振...

- [2020-07-06]時鐘網絡與OCXO振蕩器的階層級別...

- [2020-06-22]Jauch公司專門為導航開發的新TC...

- [2020-06-06]解鎖Statek振蕩器系列產品的品質...

- [2020-05-28]VV-800系列VCXO晶體振蕩器的包裝...

- [2020-04-30]獨家推薦MEMS振蕩器應用電機系統...

- [2020-04-25]海外各大元件供應商紛紛停工,是...

業務經理

業務經理 客服經理

客服經理